Build Gates

Overview

Cadence supplies Build Gates as its synthesis tool. A synthesis tool takes a high level circuit description, Verilog or VHDL, and turns it into a netlist consisting of building blocks defined in a technology library. Build gates synthesizes designs into a generic technology library and then it is up to you to link the generic design to the library you created. This means that you have to have a standard cell library created before you can begin synthesizing designs. Don't worry, we'll supply a standard cell library for this tutorial. You won't have to make your standard cells until you get to the labs.

HDL Design

The first thing you need in order to synthesize a design is the design. This tutorial uses a simple four bit counter as its design.

Create a directory to hold the synthesis output files from build gates.

mkdir synthesis

cd synthesis

Download or copy the counter file into your synthesis directory.

Timing Library File

A timing library file (.tlf) describes rise times, fall times, propagation delays, input and output capacitances, and other standard cell attributes. The synthesizer uses this information to optimize the synthesis process and to choose the correct cells from your library. Timing library files are created by the standard cell library designer. The tutorial provides you a .tlf file but you'll need to create your own based on your own standard cells.

Put this timing library file in your synthesis directory. Note, this was generated using syn2tlf on UT_LP_AMI06.lib

Build Gates Extreme

Cadence bundles three synthesis tools. Build Gates, Physically Knowledgeable Synthesis and Build Gates Extreme. Build Gates Extreme bundles the other two tools and also adds some functionality. Whenever you are referred to Build Gates in the documentation, assume it means Build Gates Extreme.

To start the tool, navigate to your synthesis directory and type:

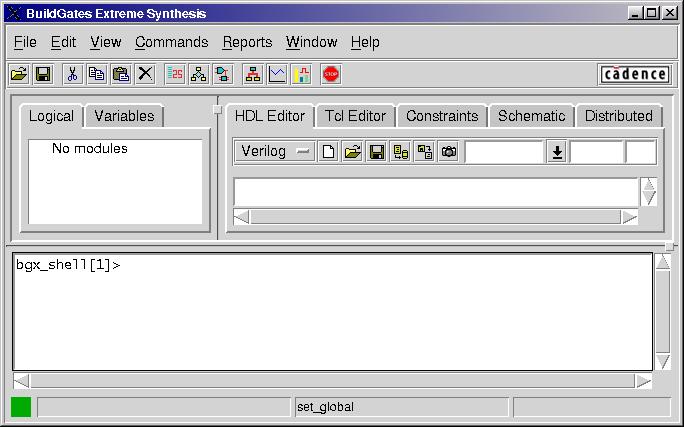

bgx_shell -gui &

You should see the gui window open up.

The most important window for you is the command window. (It's the one on the bottom of the screen.) Enter the following commands to synthesis the counter design.

read_tlf UT_LP_AMI06.tlf

read_verilog ctr.v

do_build_generic

set_top_timing_module ctr

set_current_module ctr

do_optimize

write_verilog ctr.op.v

You should now have a file in your synthesis directory that looks like this: ctr.op.v.

The following section breaks down each build gates command.

read_tlf UT_LP_AMI06.tlf - Read a .tlf file. In this case read in the sample file supplied by the tutorial. This library only has four devices, nand2, nor2, inv and a d-type flip flop. This command must come before the do_optimze command. To check the results of reading in the library type report_library and read about the components found in the library.

read_verilog ctr.v - Read in a verilog file. You can read in as many verilog files as you need to in order to import the entire design. Read the files in on the same line or issue a separate read_verilog line for each file. Likewise, read_vhdl reads a vhdl file.

do_build_generic - Builds a generic netlist of your design using the Ambit gate library. This library has no layout or schematic information saved in cadence. You need to go from the Ambit library to your target library by issuing the do_optimize command. The reason for the intermediate step is that you can specify different architectures for common components using the Ambit library. For instance, if you have a statement in your verilog code that instantiates an adder, it is in the Ambit library step that you specify ripple carry, carry propagate, carry look ahead or whichever architecture you wish to use. Then, during the optimize step, that architecture is created using your standard cells.

set_top_timing_module ctr - Set the top timing module to ctr. The default is to set the top timing module to top. You want to run the optimizer on your actual design, so you need to make sure the tool is pointing at your design before optimizing.

set_current_module ctr - Set the current module to ctr. The default module is top, you want to run the optimizer on your design, so make sure the tool is pointing at it before running the optimizer.

do_optimize - Create a circuit using the target library instead of the Ambit library. Optimize the circuit based on any constraints set. No, we did not specify any constraints for our design. Constraints usually take the form of clock rate and area. More on this later.

write_verilog ctr.op.v - Write a verilog file of your synthesized design. This file is completely structural, instantiating and specifying gates and wire interconnects. Note, make sure you don't write this out to the default file, you will overwrite your original and won't be able to ensure that the synthesis worked correctly.

Back to Virtuoso Schematic

Now that you've successfully synthesized your design you need to import it back into Virtuoso Schematic so that you can verify that Build Gates synthesized a circuit with the same functionality as your original design. These steps will work, but because you do not have the UT_LP_AMI06 library in your directory you will not be able to import the design. When you do this for your standard cell library, just remember to replace UT_LP_AMI06 with whatever your standard cell library is called.

Navigate to your cadence directory.

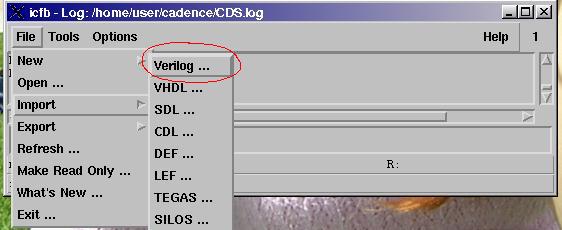

Go to File -> Import -> Verilog...

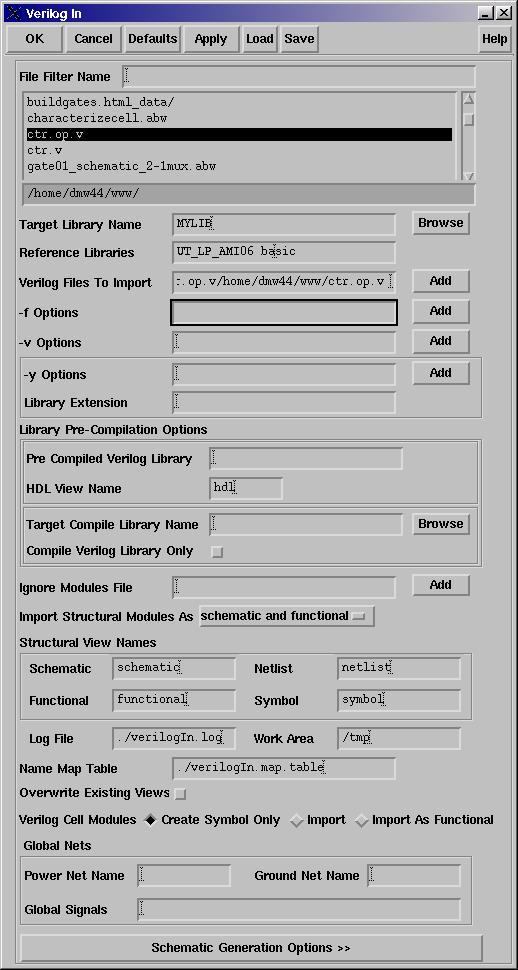

Fill in the following information. Note, if you want to learn more about the verilog import options, look up the import screen in the documenation.

Target Library Name: Library containing your designs. This is the place the import tool will put the design.

Reference Libraries: Libraries containing the parts in your design. In this case we only used parts from the UT_LP_AMI06 library. Delete sample from the list and add UT_LP_AMI06. Don't delete basic, but make sure it is the last library in the list.

Verilog Files To Import: ctr.op.v. This is your synthesized verilog file.

Import Structural Model As: schematic and functional

Leave the default values for the rest of the fields.

Press OK.

You should now see a ctr cell in your library with functional, schematic and symbol views. At this point you should simulate the synthesized design to verify it works exactly the same as the behavior version.

Conclusion

You now know how to use Cadence's synthesizer Build Gates. To better optimize your design you need to learn more about the constraints capabilities. See the Build Gates user manual for more information.