The standard cell library we are creating needs to be integrated with the cadence synthesis tool,build gates. In order for build gates to correctly synthesize your circuit it needs to know timing and loading information about the standard cells in the library. You will need to generate simulation data in order to write your technology library.

We will write the technology file in the file format created by Synopsis using this sample technology file. The reason for this is that the synopsis technology file format is much more readable than the build gates technology file format. After writing the synopsis style technology file we will translate it to the style build gates expects by using the translation tool.

Note: Emacs nicely highlights the syntax in this file if you turn on c-mode. Another note: this sample technology file wasn't made for the geometries we are using in class. While the format and generic parameters in the file will not change, the specific capacitance and timing information will. The final section of this document explains every section of the technology library file. Because a few of the sections are harder to generate data for, we will focus on them more exhaustively. They are the sections you need to customize: the capacitive load unit, the delay threshold points and the cell function.

Within the technology file, you will have to include the relative

capactive load of each pin. This is a simple matter of

calculating the

area of your transistor from your layout and plugging it into the

equation.

The capacitive load unit lets us define all the capacitances in the circuit in terms of the standard load which is defined as four inverters. Every cell defines its pin capacitance in terms of this load. If you look at the inverter section of the technology library you will see that the input capacitance on pin A is 0.25, one quarter of the standard four inverter load.

Let's calculate the capacitive load unit for our standard cell library. The input pins of a standard cell connect to the gate of one or more nmos and/or pmos transistors. An oxide layer insulates the gate poly layer from the substrate creating a capacitor. Mosis reports process parameter results from fabrication processes and from these reports we know the value of gate oxide capacitance per unit area for the AMI ABN process isThe total capacitance at an input pin is the sum of the areas (W*L of the transistor gates multiplied by Cgox). The inverter input pin, A, is connected to both nmos and pmos transistors with dimensions W/L=3.6/1.2 (nmos) and W/L=10.8/1.2 (pmos).

The total capacitance equals

CpinA=[(W1*L1) + (W2 + L2)]Cgox

= [(3.6*1.2) + (10.8*1.2)]*1.1*10^-15

= 0.019*10^-12

Calculating the standard capacitive unit load simply involves calculating the input capacitance for an input pin connected to four inverters.

Cstandardload= 4*CpinA = 0.076*10^-12

The normalized capacitance of a single inverter is therefore

CpinA(normalized)=0.019pf/0.076pf = 0.25.

When calculating your pin capacitances:

1.) Determine how many transistors the pin connects

to.

2.) Add up the areas of the transistor gates.

3.) Multiply by Cgox =1.1

4.) Divide by the capacitive unit load Cstandardload=0.076*10^-12

The synthesis tool uses these times along with the capacitance of

the standard load to calculate the rise and fall resistances. Rise and

fall timing measurements fit into two categories, propagation times and

slew rates. The technology library uses intrinsic rise and fall to

record propagation times and it uses rise and fall resistance to record

slew rates. This section describes the post layout simulation

environment used to measure intrinsic rise, intrinsic fall, rise

resistance and fall resistance.

A) Test Library The first thing you need to do is create a new library called testLib. It will contain all the schematics you use for testing your standard cells. Link the library to the AMI12 technology library. Create a cell called test for your timing measurements. Also, remember to change the model types of the transistors to ami12N and ami12P.

B) Propagation Rise and Fall

When characterizing a cell's propagation delay, use the setup in Figure 1. Choose vpulse and vdc from the NCSU Analog parts. Set the source parameters as follow:

Voltage 1 = 0V

Voltage 2 = 5V

Delay time = 0ns

Rise time = 2ns

Fall time = 2ns

Pulse width = 25ns

Period = 50ns

Your schematic should look similar to the one below. Notice the inverter in the test setup. It is used to simulate a real driving device and should use the schematic cell view. It should be connected to the input you are testing, while the other inputs can be held as non-controlling inputs. For NAND logic this is high, and for NOR logic this is low - just think about what way you would have to hold the other inputs so that the input you toggle will toggle the output. The second device is the part being tested and should use the analog extracted view.

In the Library Manager window, create a

new cell view for the invertersim cell. Go to File -> New -> Cell

View ... In the Create New File window that appears, type config in the

"View Name" field and the "Tool" field should automatically change to

Hierarchy-Editor. If not, change the "Tool" field manually. Select OK.

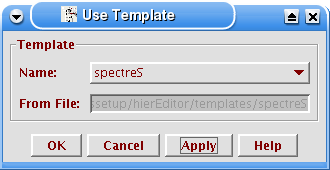

Two windows will appear. In the New Configuration window, select Use Template, and select "spectreS" in the "Name" field drop-down list. Select OK.

Make sure that the library is testLib, the cell is the name of the test schematic you created, and the view is schematic. The global bindings should also have appeared.

The following window will have appeared. Right click on the device you are testing and select Set Instance View -> analog extracted.

You can also change the view to tree mode by selecting view->tree.

Save and close the config window and from your schematic select Tools -> Analog Environment.

From the window that appears, you will be editing three setup conditions: Design, Simulator/Directory/Host, and Model Path. First, go to Setup -> Design. Choose the the test that you are running and select View Name to config.

Next change the simulator to spectreS by going to the Setup -> Simulator/Directory/Host window. Make sure it looks like the following:

Next change add the model path that contains the AMI12P.m and AMI12N.m files. Go to Setup -> Model Path. Type in /ee2/Cadence/local/designkits/BYU/lib/AMI12/models/spectreS. Click the add button.

Now from the Analog Environment window, go to Analyses -> Choose, and select transient with an amount of time to run. It should be at least two times the period of your longest vpulse.

To select what signals you want to view,

go to Outputs -> To Be Plotted -> Select on Schematic. Select the output and the input you are toggling (after the inverter buffer).

Now run the simulation by clicking on

the green light button.

For instance, to test B, hold A high and toggle B. Likewise, to test A hold B high and toggle A. Refer to the sample technology library file, notice how pin Out has a timing section related to pin A? Each input pin has its own timing section in the output pin section of the cell definition. If this were a nand gate, the output pin section would have two timing sections, one related to pin A and one to pin B.

C) Rise and Fall Resistance

Measure the rise and fall resistances by removing the noLoad output from the device under test (DUT), wiring the inv to the output of the DUT and creating a new output pin on the output of the DUT called Load. Name the wire in between the DUT and the output. Run the simulation again and this time measure the 10-90 rise and fall times of the DUT. Record these for use in the technology library file. Similarly to the propagation time measurements, each input pin is timed separately for the resistance measurements.Create the File

You should put your technology file in your standard cell library folder. Navigate to the folder named stdCellLib and use your favorite text editor to create a file called stdCellLib.lib. By now you have an example of a technology library file and a good idea of what goes in one. We are going to write the library portion for your file as well as the inverter section. As a side note, you only need one file for your entire library. As you create and add more cells to the library, simply add a new cell definition section for each new cell.

Write the File

voltage_unit : "1V";

current_unit : "1mA";

pulling_resistance_unit :"1kohm";

time_unit : "1ns";

capacitive_load_unit(0.076,pf);

Remember to select the units so that they are consistent with each other. Note that in the library there is no direct way to specify the resistance unit. When we calculated rise resistance and fall resistance we specified them in nanoseconds. Using a similar approach make sure the other units are consistent with each other.

Realize that 0% always corresponds to logic '0' and 100% always corresponds to logic '1'. If not specified the default value is 50%.

The other option is no swapping.

/* inverter cell */

cell(INV) {

:

:

}

Each cell describes cell level simple attributes and pin groups with specific timing information.

area : 550.8;

As discussed earlier in Cell Swapping Criteria, cells with identical pin names and functionality but different characteristics are identified by the same value for the attribute. Specify the inverter family by settingcell footprint inverter.

cell_footprint : "inverter";

A and Y. Pin A sees the gates of an nmos transistor and a pmos transistor, both of which contribute to its gate capacitance. We calculated this earlier. Here the capacitance is recorded in terms of the standard 4x inverter load, which makes a single inverter input's capacitance 0.25. The output pin does not internally connect to any transistor gates, therefore it does not record any pin capacitance. If it did internally connect to a transistor gate then specify its capacitance similarly to the input pin's capacitance.

pin(A) {

/* pin level simple attributes */

direction : input;

capacitance : 0.25;

}

pin(Y) {

/* pin level simple attributes */

direction : output;

:

:

}

The function attribute in the cell definition section of the technology library file defines the functionality of the cell. The synthesis tool, build gates, uses the function to correctly construct the operation you code in your verilog. Write the functions for your logical gates using the operators in Table 1.

A couple examples, the inverter has the function !A, a NAND gate would have the function !(A&B). Describing functionality of sequential cells is more complicated and is described in detail at the website above.

Table 1: Cell Function Operators

| ' | invert previous expression |

| ! | invert following expression |

| ^ | logical XOR |

| * | logical AND |

| & | logical AND |

| space | logical AND |

| + | logical OR |

| | | logical OR |

| 1 | signal tied to logic |

| 0 | signal tied to logic 0 |

Cell Timing

You should now have a stdCellLib.tlf file in your directory. Congratulations, you are almost through the tutorial!

module cell1_name (out1, out2, ... , in1, in2, ...); A verilog interface file for the stdCellLib with only one

inverter cell looks like this:

output out1, out2, ...;

input in1, in2, ...;

endmodule

module cell2_name (out1, out2, ... , in1, in2, ...);

output out1, out2, ...;

input in1, in2, ...;

endmodule

:

:

module celln_name (out1, out2, ... , in1, in2, ...);

output out1, out2, ...;

input in1, in2, ...;

endmodule

module INV ( Y, A );

output Y;

input A;

endmodule

Make a file in your stdCellLib directory called stdCellLib.v. Add the inverter cell to it. As you add additional cells to your library, make sure to include a module for each in the verilog interface.

Creating a standard cell, characterizing it, recording all the data in the technology library file and writing the verilog interface is a long process. Refer to this file often as you create more cells for your library.

Remember that cell library creating simplifies your life later by allowing you to write your circuits in an HDL and synthesize them without resorting to k-maps, state diagrams, schematic capture and lots of headaches when you need to redesign. As always, if you have any trouble or find any errors in this tutorial let the TAs and the professor know.